electrical engineering / mixed-signal ic design

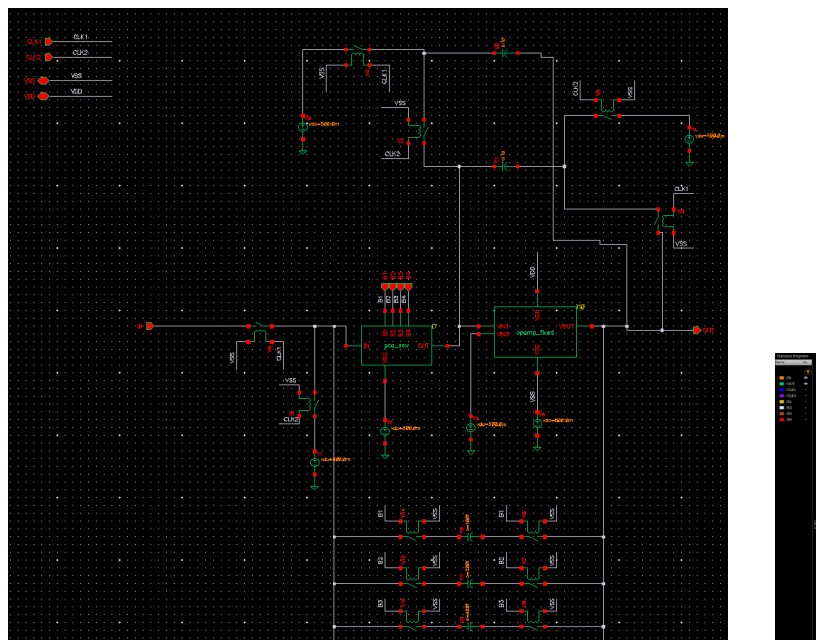

Mixed-Signal ECG Front-End IC

problem

How do you acquire low-amplitude ECG signals and digitize them on-chip under a strict 1 V, low-power constraint?

Cadence VirtuosoSpectreVerilog-Amixed-signal simulation

what i did / what shipped

I designed and verified the analog chain end-to-end, from mux and PGA through op-amp and SAR ADC, then documented the final system in a full report.

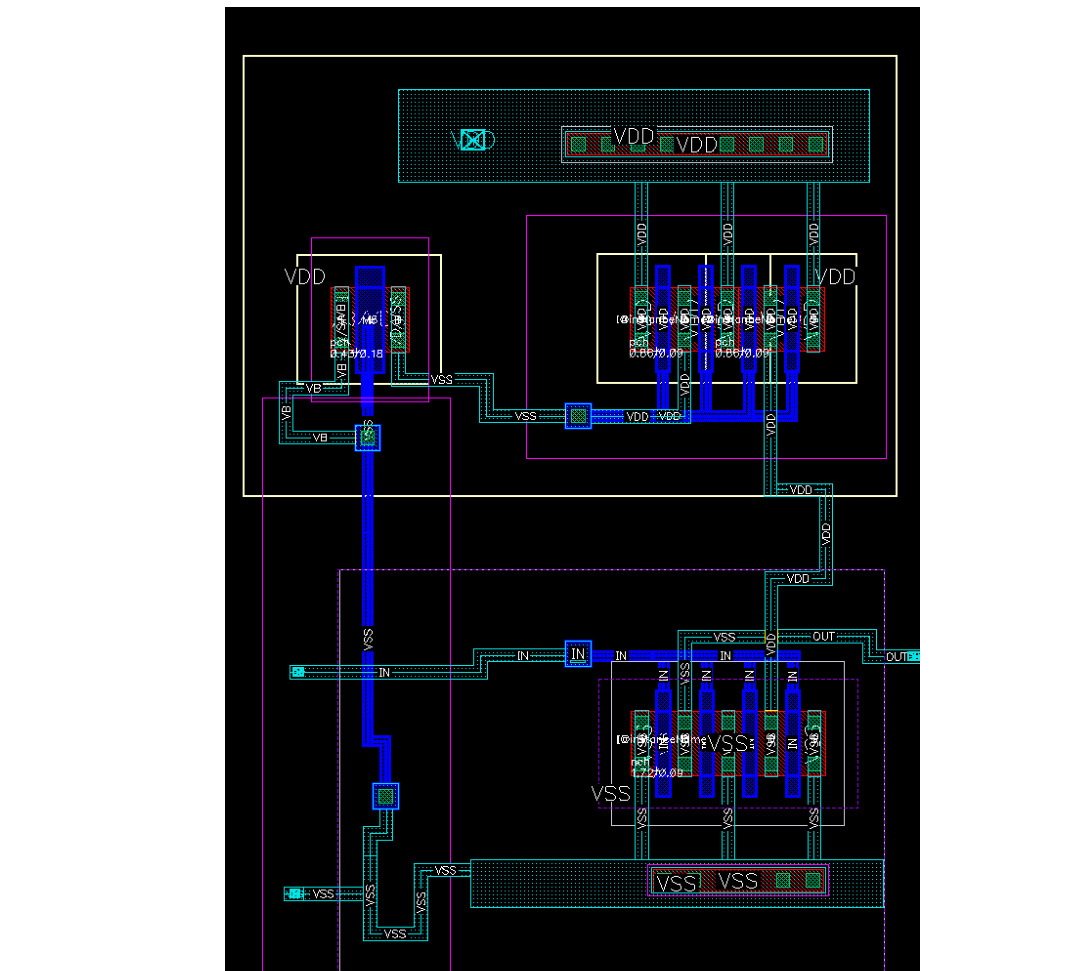

electrical engineering / physical design

Analog Front-End Layout & Verification

problem

How do you carry an analog design through layout, DRC, LVS, and extraction without losing the behavior that mattered at schematic level?

Cadence VirtuosoCalibrefull custom layoutpost-layout analysis

what i did / what shipped

I completed layout, rule closure, extraction, and post-layout comparison so the design was validated as both geometry and electrical behavior.